Hans Kurscheidt

Members-

Posts

37 -

Joined

-

Last visited

Recent Profile Visitors

The recent visitors block is disabled and is not being shown to other users.

-

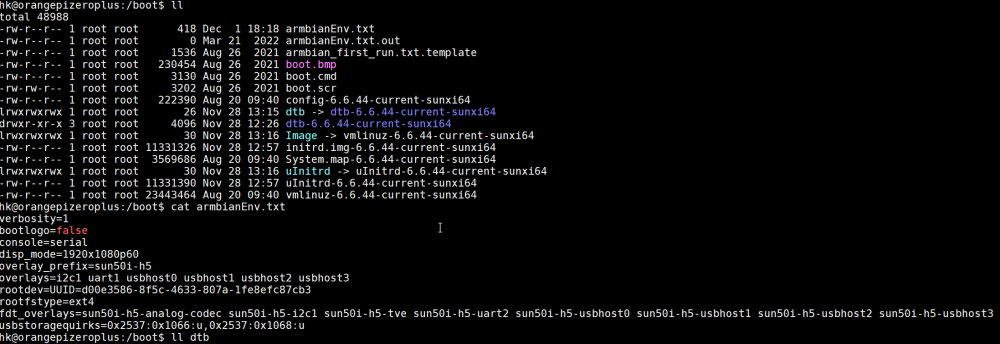

armbian-config has significantly changed in Bookworm/Kernel 6.6. It looks to me that its not reflecting the actual device settings. Please refer to the attached screenshot from /boot/armbianEnv.txt. Compared to Bullseye/Kernel 6.1.92 I see an additional line "fdt_overlays, where all the dtb settings from the new armbian-config appear, fdt_overlays=sun50i-h5-analog-codec sun50i-h5-i2c1 sun50i-h5-tve sun50i-h5-uart2 sun50i-h5-usbhost0 sun50i-h5-usbhost1 sun50i-h5-usbhost2 sun50i-h5-usbhost3 but they seem to not having any effect. In 6.1.92 this line does not exist. The real dtb settings are still in the line above overlay_prefix=sun50i-h5 overlays=i2c1 uart1 usbhost0 usbhost1 usbhost2 usbhost3 which is identical in 6.1.92 and 6.6.

-

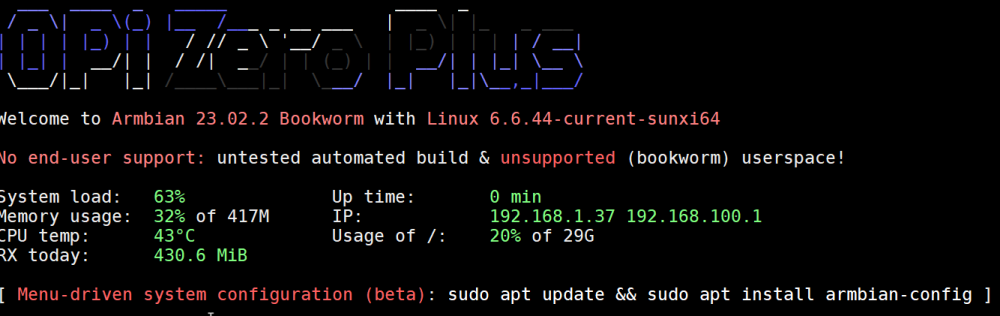

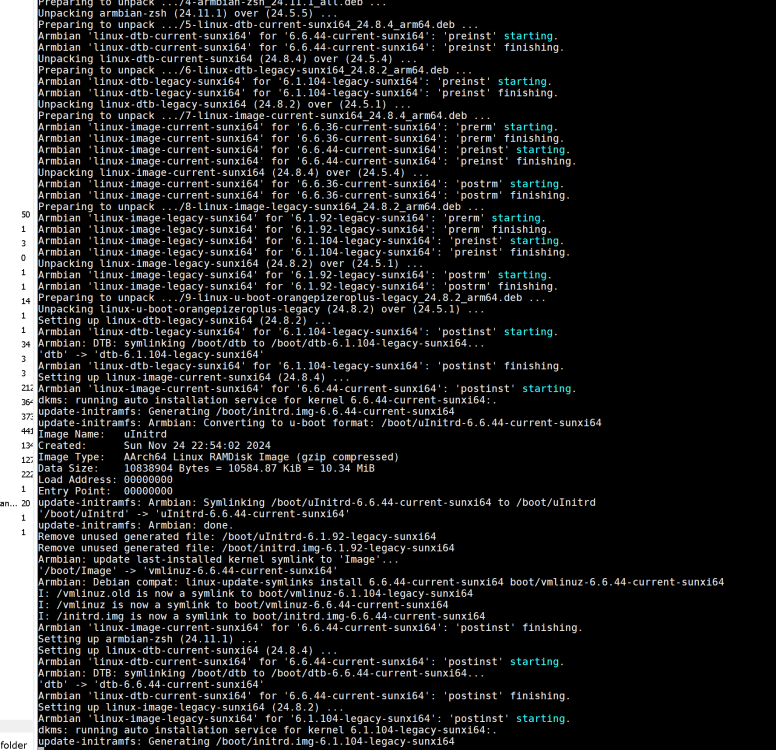

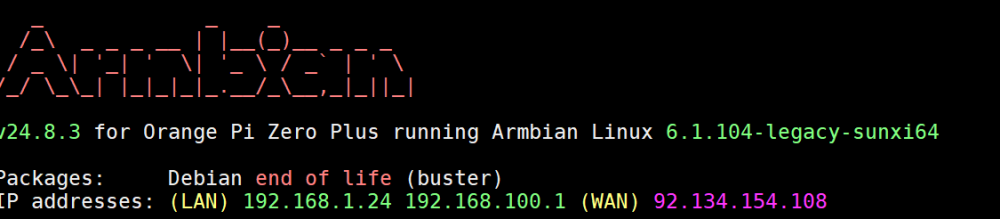

OK, so I'm there! but rather than doing a fresh install, I used the following method: using armbian-config under kernel 6.1.92 to unfreeze using armbian-config to switch to "other kernel" -> 6.6.44 That worked OK and gave me Debian Bullseye w/ kernel 6.6.44 I then edited /etc/apt/sources.list and /etc/apt/sources.list.d/armbian.list, replacing Bullseye w/ Bookworm. I then started apt-get update/upgrade. After a huge upgrade I ended up w/ Debian Bookworm, but had fallen back to kernel 6.1.104. I then applied the method as described by robertoj to finally get Debian Bookworm w/ kernel 6.6.44

-

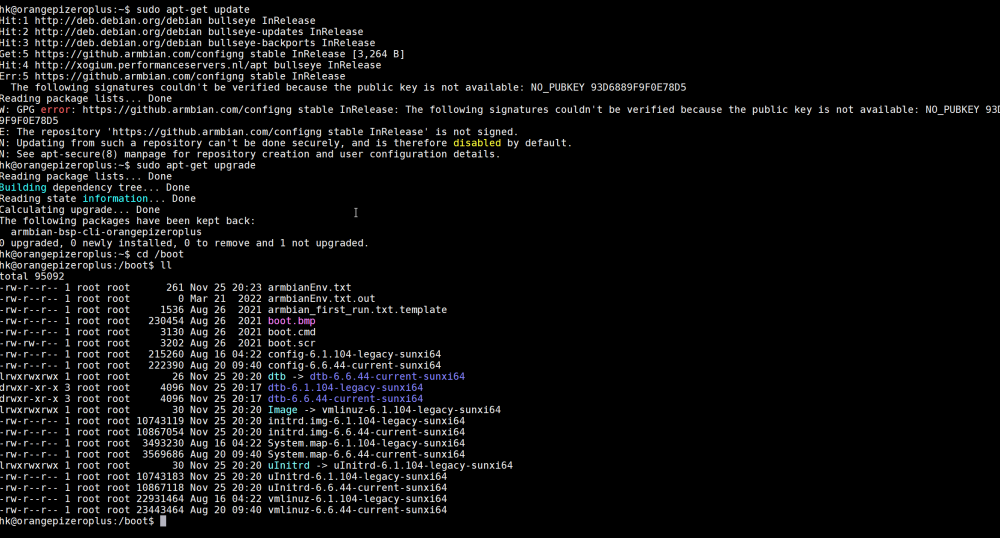

Well, I tried my very best to find a solution, just to run into other Armbian peculiarities. 1st, the problem with the missing signature can be solved by telling apt to ignore it. Hence I created my apt.config settings in /etc/apt/apt.config.d as following: cat 99mysettings Acquire::AllowInsecureRepositories "1"; Acquire::AllowWeakRepositories "0"; Acquire::AllowDowngradeToInsecureRepositories "1"; So apt started to work on it, giving the appropriate warnings: which I ignored, so it started the upgrade: just to learn, that I'm stuck again w/ Armbian. something w/ "unknown compression"

-

I'm sorry, but you misinterpreted the screenshots. Please refer to my 1st line in my 1st post: >>>>I had to freeze my device on Kernel 6.1.92 & Bullseye to remain operational. Now trying to update/upgrade to Kernel 6.6.nn <<<< I was always on Bullseye since years now and Kernel 6.1.92 frozen since early this year. Trying to move from 6.1.92 to 6.6.42 (switching kernel after defreeze in armbian-config) created a mess including throwing me back onto Buster, God knows why and how! May be, that I am using a code that is not supported on a hardware that is not supported, but normal Linux' way of upgrade should still work and for the time being, I am almost sure, that the upgrade doesn't work, because you guys haven't created the proper public key for apt.security to accept the upgrade. RGDS hk

-

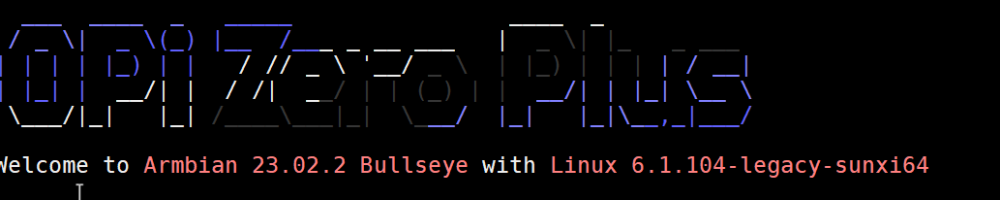

Hi there, as expected, in my frozen image, they are pointing to 6.1.92. After unfreeze and apt-get update/upgrade I'm now lifted to 6.1.104 & Bullseye However its not want I want, 6.644. a new issued apt-get update/upgrade has no effect. looks like a security issue to me, now. https://github.armbian.... is not signed RGDS hk

-

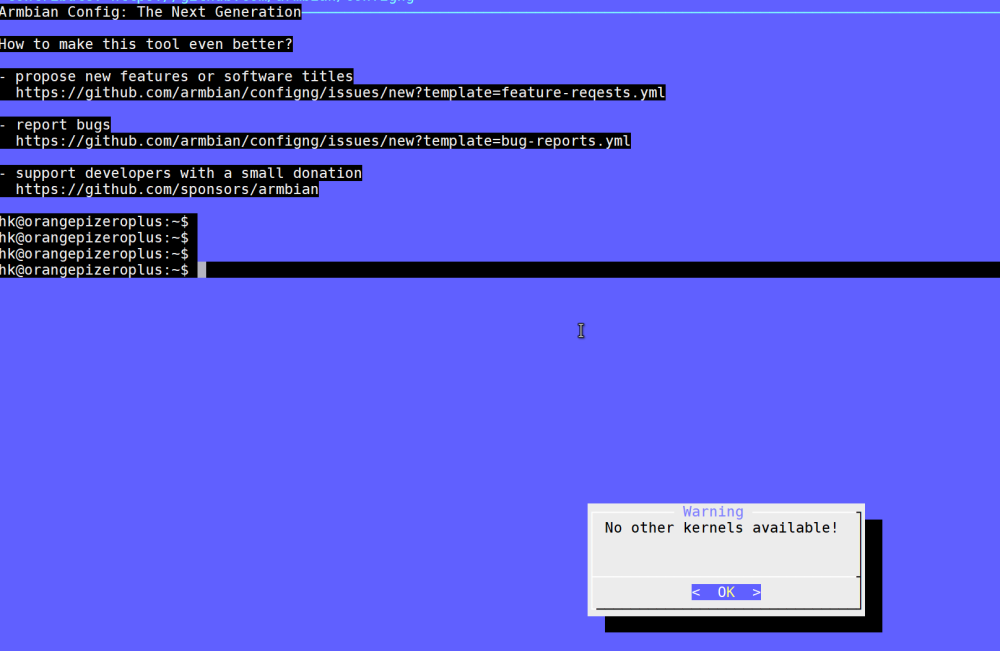

Thank-you for reply. Sorry for the beginners question, but "How to"? I used armbian-config to move from 6.1.92 to 6.6.44 and I was assuming that 6.6.44 would replace 6.1.92; apparently it did not, as you said in your reply. So how can I make 6.6.44 the new 1 and only new kernel. I currently back to my old image w/ kernel 6.1.92 frozen and Debian Bullseye. I have a complex APP with tons of middleware and 3rd party SW; a fresh new installation would be a PITA.

-

I had to freeze my device on Kernel 6.1.92 & Bullseye to remain operational. Now trying to update/upgrade to Kernel 6.6.nn I run into following probs: 1) Using Armbian-config defreeze and subsequently switch to kernel 6.6.nn works OK 4me, but subsequent apt-get update/upgrade throws me back to kernel 6.1.104. Armbian-config has changed significantly w/ No other Kernel available. 2) Using Armbian-config defreeze, only and going directly to apt-get update/upgrade throws me back to kernel 6.1.104 as well and from Bullseye back to Buster! Its a mess! Will this eventually be corrected and when? RGDS