Search the Community

Showing results for 'tv'.

-

Hello Im running home asistant supervised on Debian GNU/Linux 12 (bookworm). Docker 28. On a T95Q S905x2 tv box. I have error message : overlayfs: NFS export requires "redirect-_dir=nofollow". on non upper mount falling back to "NFS export=off" Well dont know any programming. only CTRL C + CTRL V. Its some directory debian cannot access on th Tv box. Can yo help me please? Kind Regards Zsolt

-

Using the composite video output on the bananapi M1

Ryzer replied to DavidMF's topic in Allwinner sunxi

@robertoj In terms of the actual TV encoder itself not significantly different, the same TV encoder driver is used for the H3. It just parses a different compatibility string to address any differences. If it still works on a device like the Orange Pi Zero then that is strong indicator that it is likely to work on the Banana Pi M1 Another thing to be mindful of is that the TV encoder is only part of the Display Engine. The A10 and A20 (which is the SOC on the Banana Pi M1) both have the 1st generation Display Engine where as the H3 is based on the 2nd generation. -

Using the composite video output on the bananapi M1

robertoj replied to DavidMF's topic in Allwinner sunxi

Is the A10's TV encoder much different from the H3 TV encoder? The orange pi zero LTS has a working TV-out in Armbian (at least when I tried it last year) -

CSC Armbian for RK3318/RK3328 TV box boards

Víctor Álvarez replied to jock's topic in Rockchip CPU Boxes

My 2 boxes is for the moment HA in production and the second one is updated Android V1, then it was having problems running large Magis TV IPTV (corrupting the files system) that looks working OK now. -

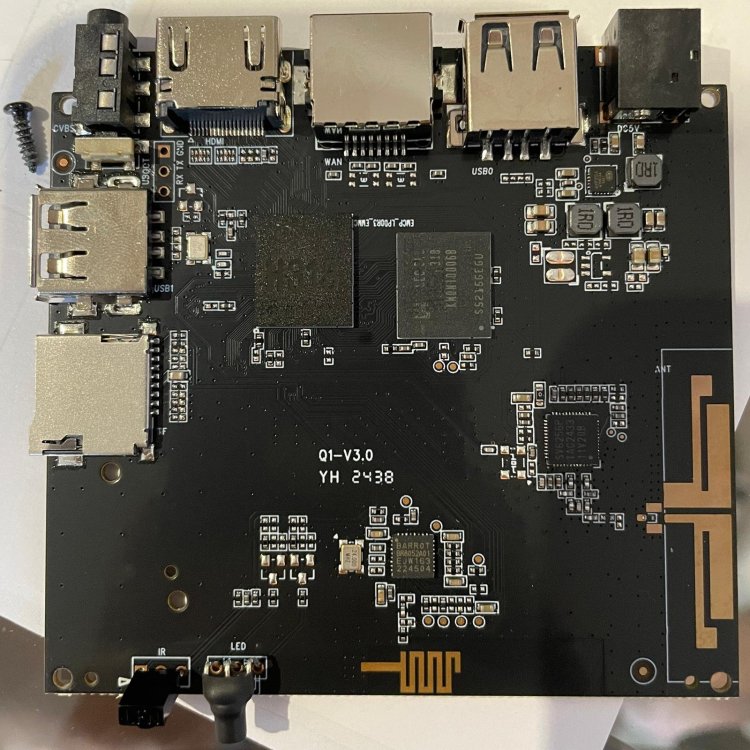

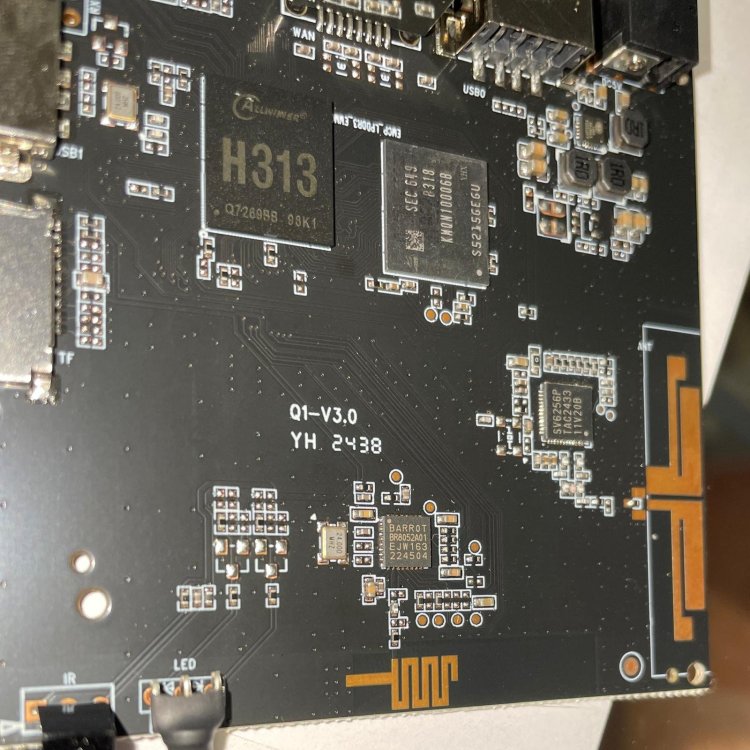

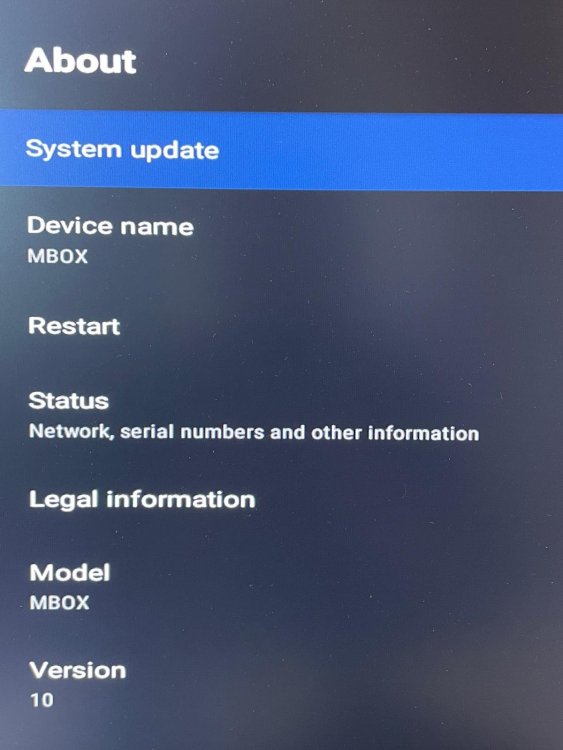

Hello everyone, I have an ATV Q1 V3.0 box running Android TV 10. Some people have put img with secure boot, but all the links are expired. Can someone provide a link for an img with secure boot please ? Thanks.

-

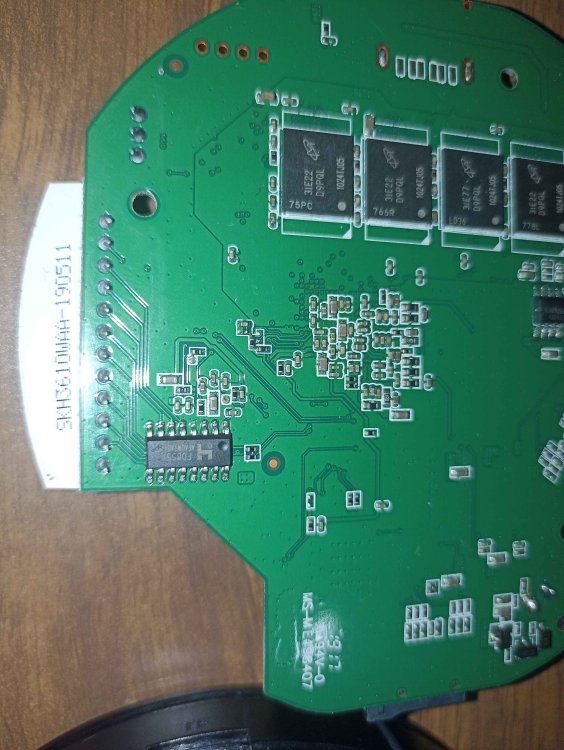

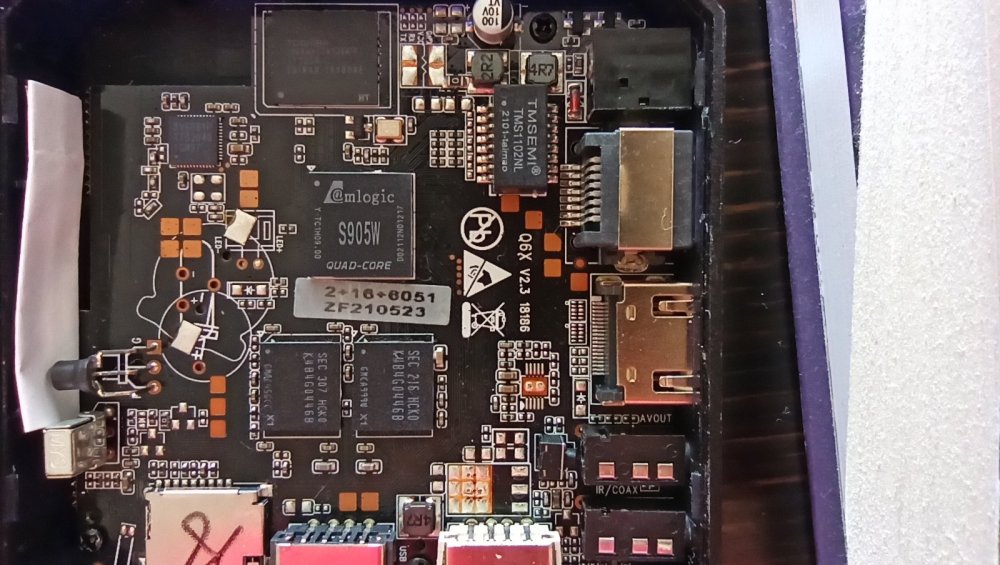

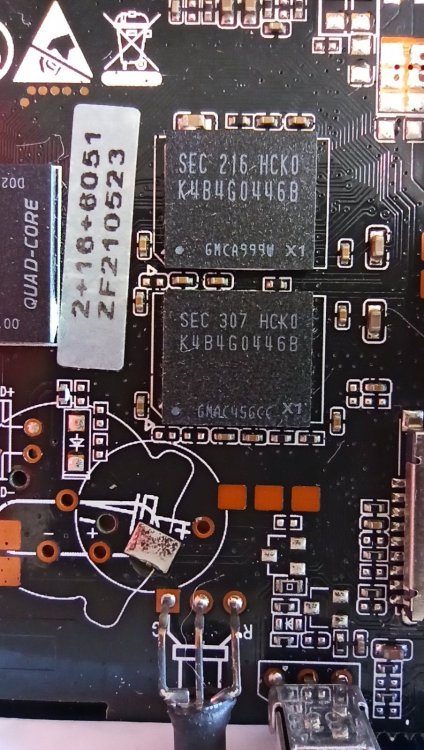

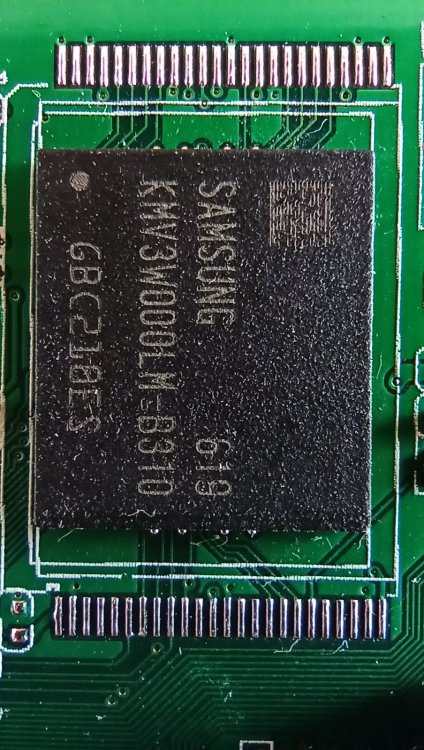

Looking to try out the capabilties of those TV Boxes with linux. Wonder if any of those two boards would work out. Seems theres no official support for either but it someone has got one of those working, some help would be much appreaciated. The one from above is h313-emcp_v1.0 and the bottom one is a h20_221_v1.6_230523.

-

@jock after much suffering i was able to boot the multitool and delete the emmc image, i can now boot into the multitool without having to short the pads. Now... i need to find a suitable image for my board... Downloading... Armbian_community_25.5.0-trunk.87_Rk3318-box_bookworm_current_6.12.15_minimal.img Flashing.... Done... Booting.... HOLY it worked lol! Im at the login screen... im guessing the default is something like "root" "1234" or similar. Now i need to write the image to the emmc... EDIT: The image seems to work but for some reason when connected to my tv i tried to connect to wifi and the image started to stutter i couldn't get it to connect to wifi but it did see my network. weird... need to keep trying i guess

-

Using the composite video output on the bananapi M1

Ryzer replied to DavidMF's topic in Allwinner sunxi

Hi David, Can you check that sun4i-a10-tv-encoder module is present with lsmod? If it is then you will probably need to edit the device tree to include the TV display nodes, the bindings can be found here: https://web.git.kernel.org/pub/scm/linux/kernel/git/stable/linux.git/tree/Documentation/devicetree/bindings/display/allwinner,sun4i-a10-tv-encoder.yaml?h=v6.12.17 If not you can try to build the module if you have headers installed. Unfortunately I don't know the status of tv output support so there is a possibility even carrying out each of these steps that it may not. Best of luck Ryzer -

@ROOD your board (YX_RK3328) should be already supported by rk3318-box image. The "marketing name" of the TV Box means nothing, the only important discriminant is the board name printed on the PCB. Anyway you made two mistakes: took the image from an unkown source burnt a non-working image in eMMC Now your only chance to restore board functionality is to go in maskrom mode: eMMC is always first priority, so you don't have any chance to boot from SDcard if a image that does not boot is stored in eMMC.

-

Using the composite video output on the bananapi M1

eselarm replied to DavidMF's topic in Allwinner sunxi

Show U-Boot + kernel version. and maybe much more. My M1 is unused at the moment, I will connect some SATA disk soon, but I don't know If I still have working composite video, that is a problem. I don't have a TV, maybe a USB recording device with composite imput I have somewhere in a paperbox can be use. -

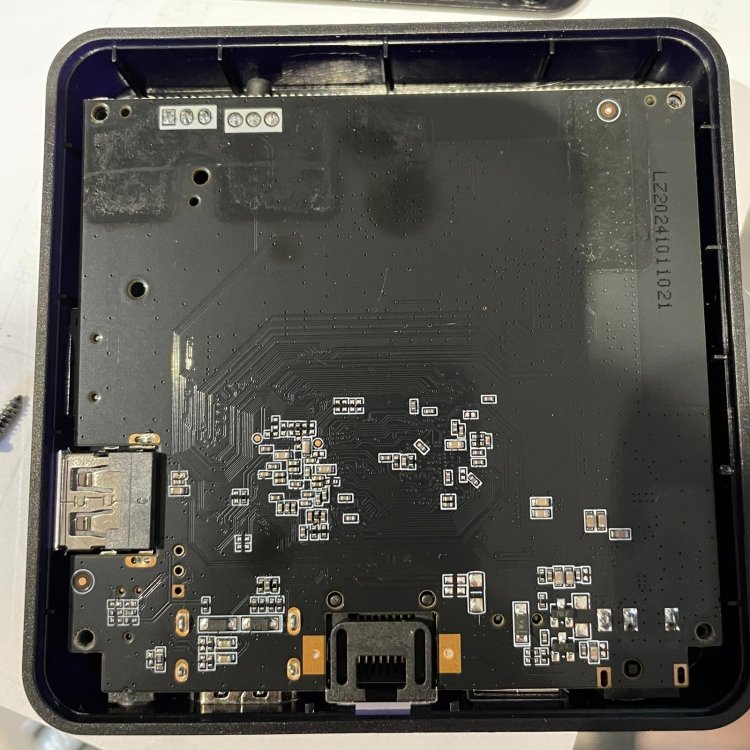

@jock Hey! Thanks for all your effort trying to bring Armbian to the TV Boxes. I wanted to ask if there was a chance to port it to the BQEEL U1 PRO, it has the RK3328 CPU. I totally screwed the flash up doing some experiments and i couldn't get the flash backup so im kinda lost on that front. I tried to download the images from the first link but every link is broken. I wonder if there is a mirror or any other way to get the images Tried searching for them elsewhere but got nothing but a very weird image This one that kind of works but it just blinks the led blue and red without any Video output. Maybe its just a dtb issue but im too new to fully understand and fix the issue Edit: I was able to boot using the Multitool and tried to burn an image to EMMC but now it doesn't boot with either option. I tried to short the pins like Constantin did here Very similar board if not the same but couldn't get it to boot, maybe im missing something.... Here are some images

-

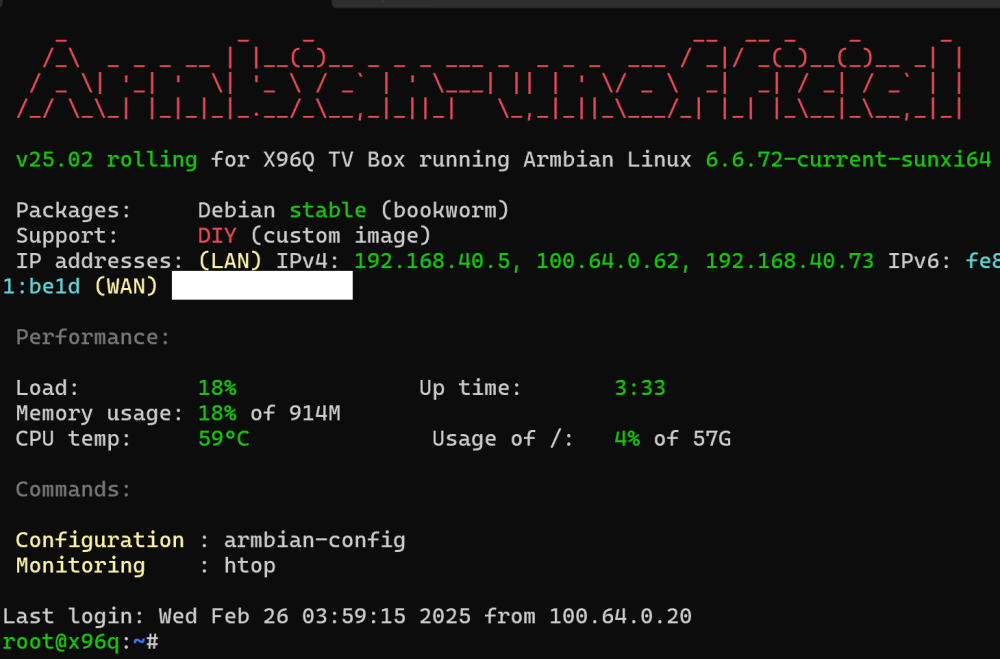

Hi @Xortes, Yes, I managed to build an Armbian image using the LPDDR3 defconfig mentioned earlier, along with the U-Boot and kernel patches suggested by @Nick A, based on the minimyth2 patch. Unfortunately, HDMI is still not working, even with the current 6.6.72 kernel. However, since I plan to use this TV box for running AdGuard Home, HDMI output isn’t essential for my use case. On a positive note, I’ve successfully got both wired and wireless networks working. I’m currently using the box as an AdGuard Home server and a Tailscale subnet router. If you’re interested, I’d be happy to share the image.

-

Help wanted to test a new OpenVFD alternative

SpellKilleR replied to Jean-Francois Lessard's topic in Amlogic meson

Good morning everyone, sorry for bothering, I'm having some trouble trying to get the display of a TV box to work correctly. The model is an X98k with RK3528a, in which I integrated the tm16xx driver into the kernel. An AiP1628 chip is mounted on the board to control the display, which in the original Android dtb is managed as tm1628. The display is 7 segments with usb, card, am, pm, wifi and lan LEDs, 4 to the left and 2 to the right of the digits. By reworking the dtb a bit, the display is detected and turned on by the driver, but with some issues: of the entire grid the two LEDs in the last column never light up, as if they were not detected/counted in any way I try to rewrite the order and mapping of the digits and segments in the dtb, two segments always remain off in each digit when testing the display, when a specific segment should light up to find the mapping, several mixed segments light up instead, including part of the first LEDs. Continuing with the tool, at each step the same segments always light up instead of varying on other segments. Changing the values in the dtb changes the LEDs and segments that light up, but they behave in the same way. The module does not report any errors in the dmesg. Could it be a simple problem writing the dtb with missing compatibility parameters and mapping or could there be interfacing problems between controller and driver? If you might need some specific logs, overlays or other details, I'm available Thanks for any advice -

Is it possible to extract the DTB file from a working Android TV BOX? I'm having fun with a new TV BOX TX3 Mini with Amlogic S905L2B (I was sure to find S905W) and before asking for help I wanted to know if I can recover the DTB file from the Android image that works correctly. Thanks

-

Next Minix Mediabox 16 GB Android 11 TV Box armbian s905y4 image download please link??

-

s905y4 tvbox armbian image download please???

Energokom replied to omarxy's topic in Amlogic CPU Boxes

This soc s905y4 is already 5 years old - it is already old. I only know one person who supports linux on amlogic. Arbmian developers are not interested in support TV boxes, as it does not pay. No one is ready to work on enthusiasm. Therefore, do not wait for the support of these TV boxes. If amlogic, then I advise you to take TV boxes on soc s905x3 - armbian works on them. -

There are 2 TV boxes. I put Armbian on both, on the x96 mini you can see 2 gigabytes of RAM, but on the m9s you can see only 1 gigabyte. Physically, both have 2 gigabytes of RAM. Please tell me what can be done? x96 mini(s905w): m9s pro(s905x):

-

TX95 Max - Allwinner H618 Quadcore Cortex - A53

Mark Waples replied to Mark Waples's topic in Allwinner CPU Boxes

Hi, Nick that's great information - thank you! It all checks out. The only command that worked was: echo alarm > /sys/class/leds/openvfd/led_on This turned on the wifi-eth and usb leds all together and not blinking. I went to see what was in the device tree but the new armbian-configNG does not have the DTS editor available as in the old config tool. I don't know if there is a way of reverting back to the old tool (I froze Kernal Updates in the old tool) so it's very useful and I don't know why it has installed the new one as it does not have many features like the old config tool. I hate when things are forced upon you. So am I going to be forced to install DTC to decompile the Device Tree (DTB)? ------------------------------------------------------------------------ CONVERT dtb to dts ------------------------------------------------------------------------ dtc -I dtb -O dts /boot/dtb/allwinner/sun50i-h618-transpeed-8k618-t.dtb -o /boot/dtb/allwinner/sun50i-h618-transpeed-8k618-t.dts ------------------------------------------------------------------------ EDIT dts ------------------------------------------------------------------------ nano /boot/dtb/allwinner/sun50i-h618-transpeed-8k618-t.dts ------------------------------------------------------------------------ CONVERT (BACK) dts to dtb ------------------------------------------------------------------------ dtc -I dts -O dtb /boot/dtb/allwinner/sun50i-h618-transpeed-8k618-t.dts -o /boot/dtb/allwinner/sun50i-h618-transpeed-8k618-t.dtb I assume my tree is called sun50i-h618-transpeed-8k618-t.dtb and here is the contents of that tree /dts-v1/; / { interrupt-parent = <0x01>; #address-cells = <0x02>; #size-cells = <0x02>; model = "Transpeed 8K618-T"; compatible = "transpeed,8k618-t\0allwinner,sun50i-h618"; cpus { #address-cells = <0x01>; #size-cells = <0x00>; cpu@0 { compatible = "arm,cortex-a53"; device_type = "cpu"; reg = <0x00>; enable-method = "psci"; clocks = <0x02 0x15>; #cooling-cells = <0x02>; operating-points-v2 = <0x03>; cpu-supply = <0x04>; status = "okay"; phandle = <0x06>; }; cpu@1 { compatible = "arm,cortex-a53"; device_type = "cpu"; reg = <0x01>; enable-method = "psci"; clocks = <0x02 0x15>; #cooling-cells = <0x02>; operating-points-v2 = <0x03>; phandle = <0x07>; }; cpu@2 { compatible = "arm,cortex-a53"; device_type = "cpu"; reg = <0x02>; enable-method = "psci"; clocks = <0x02 0x15>; #cooling-cells = <0x02>; operating-points-v2 = <0x03>; phandle = <0x08>; }; cpu@3 { compatible = "arm,cortex-a53"; device_type = "cpu"; reg = <0x03>; enable-method = "psci"; clocks = <0x02 0x15>; #cooling-cells = <0x02>; operating-points-v2 = <0x03>; phandle = <0x09>; }; }; display-engine { compatible = "allwinner,sun50i-h6-display-engine"; allwinner,pipelines = <0x05>; status = "okay"; phandle = <0x3b>; }; reserved-memory { #address-cells = <0x02>; #size-cells = <0x02>; ranges; secmon@40000000 { reg = <0x00 0x40000000 0x00 0x80000>; no-map; }; }; osc24M-clk { #clock-cells = <0x00>; compatible = "fixed-clock"; clock-frequency = <0x16e3600>; clock-output-names = "osc24M"; phandle = <0x0f>; }; pmu { compatible = "arm,cortex-a53-pmu"; interrupts = <0x00 0x8c 0x04 0x00 0x8d 0x04 0x00 0x8e 0x04 0x00 0x8f 0x04>; interrupt-affinity = <0x06 0x07 0x08 0x09>; }; psci { compatible = "arm,psci-0.2"; method = "smc"; }; timer { compatible = "arm,armv8-timer"; arm,no-tick-in-suspend; interrupts = <0x01 0x0d 0xf04 0x01 0x0e 0xf04 0x01 0x0b 0xf04 0x01 0x0a 0xf04>; }; soc { compatible = "simple-bus"; #address-cells = <0x01>; #size-cells = <0x01>; ranges = <0x00 0x00 0x00 0x40000000>; bus@1000000 { compatible = "allwinner,sun50i-h616-de33\0allwinner,sun50i-a64-de2"; reg = <0x1000000 0x400000>; allwinner,sram = <0x0a 0x01>; #address-cells = <0x01>; #size-cells = <0x01>; ranges = <0x00 0x1000000 0x400000>; clock@8000 { compatible = "allwinner,sun50i-h616-de33-clk"; reg = <0x8000 0x100>; clocks = <0x02 0x1d 0x02 0x1e>; clock-names = "mod\0bus"; resets = <0x02 0x01>; #clock-cells = <0x01>; #reset-cells = <0x01>; phandle = <0x0b>; }; mixer@100000 { compatible = "allwinner,sun50i-h616-de33-mixer-0"; reg = <0x100000 0x100000 0x8100 0x40 0x280000 0x20000>; clocks = <0x0b 0x00 0x0b 0x06>; clock-names = "bus\0mod"; resets = <0x0b 0x00>; phandle = <0x05>; ports { #address-cells = <0x01>; #size-cells = <0x00>; port@1 { reg = <0x01>; phandle = <0x3c>; endpoint { remote-endpoint = <0x0c>; phandle = <0x2c>; }; }; }; }; }; gpu@1800000 { compatible = "allwinner,sun50i-h616-mali\0arm,mali-bifrost"; reg = <0x1800000 0x40000>; interrupts = <0x00 0x5f 0x04 0x00 0x60 0x04 0x00 0x61 0x04>; interrupt-names = "job\0mmu\0gpu"; clocks = <0x02 0x23 0x02 0x24>; clock-names = "core\0bus"; resets = <0x02 0x03>; status = "okay"; mali-supply = <0x0d>; phandle = <0x3d>; }; deinterlace@1420000 { compatible = "allwinner,sun50i-h6-deinterlace"; reg = <0x1420000 0x40000>; clocks = <0x02 0x20 0x02 0x1f 0x02 0x33>; clock-names = "bus\0mod\0ram"; resets = <0x02 0x02>; interrupts = <0x00 0x59 0x04>; phandle = <0x3e>; }; video-codec@1c0e000 { compatible = "allwinner,sun50i-h616-video-engine"; reg = <0x1c0e000 0x2000>; clocks = <0x02 0x29 0x02 0x28 0x02 0x33>; clock-names = "ahb\0mod\0ram"; resets = <0x02 0x05>; interrupts = <0x00 0x5d 0x04>; allwinner,sram = <0x0e 0x01>; }; syscon@3000000 { compatible = "allwinner,sun50i-h616-system-control"; reg = <0x3000000 0x1000>; #address-cells = <0x01>; #size-cells = <0x01>; ranges; phandle = <0x23>; sram@100000 { compatible = "mmio-sram"; reg = <0x100000 0x18000>; #address-cells = <0x01>; #size-cells = <0x01>; ranges = <0x00 0x100000 0x18000>; phandle = <0x3f>; scpi-sram@17c00 { compatible = "arm,scp-shmem"; reg = <0x17c00 0x200>; phandle = <0x40>; }; }; sram@28000 { compatible = "mmio-sram"; reg = <0x28000 0x30000>; #address-cells = <0x01>; #size-cells = <0x01>; ranges = <0x00 0x28000 0x30000>; phandle = <0x41>; sram-section@0 { compatible = "allwinner,sun50i-h616-sram-c\0allwinner,sun50i-a64-sram-c"; reg = <0x00 0x1e000>; phandle = <0x0a>; }; }; sram@1a00000 { compatible = "mmio-sram"; reg = <0x1a00000 0x200000>; #address-cells = <0x01>; #size-cells = <0x01>; ranges = <0x00 0x1a00000 0x200000>; phandle = <0x42>; sram-section@0 { compatible = "allwinner,sun50i-h616-sram-c1"; reg = <0x00 0x200000>; phandle = <0x0e>; }; }; }; clock@3001000 { compatible = "allwinner,sun50i-h616-ccu"; reg = <0x3001000 0x1000>; clocks = <0x0f 0x10 0x00 0x10 0x02>; clock-names = "hosc\0losc\0iosc"; #clock-cells = <0x01>; #reset-cells = <0x01>; phandle = <0x02>; }; dma-controller@3002000 { compatible = "allwinner,sun50i-h616-dma\0allwinner,sun50i-a100-dma"; reg = <0x3002000 0x1000>; interrupts = <0x00 0x2a 0x04>; clocks = <0x02 0x2a 0x02 0x32>; clock-names = "bus\0mbus"; dma-channels = <0x10>; dma-requests = <0x31>; resets = <0x02 0x06>; #dma-cells = <0x01>; phandle = <0x18>; }; efuse@3006000 { compatible = "allwinner,sun50i-h616-sid\0allwinner,sun50i-a64-sid"; reg = <0x3006000 0x1000>; #address-cells = <0x01>; #size-cells = <0x01>; phandle = <0x43>; thermal-sensor-calibration@14 { reg = <0x14 0x08>; phandle = <0x25>; }; cpu-speed-grade@0 { reg = <0x00 0x02>; phandle = <0x38>; }; }; watchdog@30090a0 { compatible = "allwinner,sun50i-h616-wdt\0allwinner,sun6i-a31-wdt"; reg = <0x30090a0 0x20>; interrupts = <0x00 0x32 0x04>; clocks = <0x0f>; phandle = <0x44>; }; pinctrl@300b000 { compatible = "allwinner,sun50i-h616-pinctrl"; reg = <0x300b000 0x400>; interrupts = <0x00 0x33 0x04 0x00 0x34 0x04 0x00 0x35 0x04 0x00 0x2b 0x04 0x00 0x36 0x04 0x00 0x37 0x04 0x00 0x38 0x04 0x00 0x39 0x04>; clocks = <0x02 0x1a 0x0f 0x10 0x00>; clock-names = "apb\0hosc\0losc"; gpio-controller; #gpio-cells = <0x03>; interrupt-controller; #interrupt-cells = <0x03>; vcc-pc-supply = <0x11>; vcc-pg-supply = <0x12>; vcc-ph-supply = <0x12>; vcc-pi-supply = <0x12>; phandle = <0x14>; rgmii-pins { pins = "PI0\0PI1\0PI2\0PI3\0PI4\0PI5\0PI7\0PI8\0PI9\0PI10\0PI11\0PI12\0PI13\0PI14\0PI15\0PI16"; function = "emac0"; drive-strength = <0x28>; phandle = <0x45>; }; i2c0-pins { pins = "PI5\0PI6"; function = "i2c0"; phandle = <0x20>; }; i2c2-ph-pins { pins = "PH2\0PH3"; function = "i2c2"; phandle = <0x46>; }; i2c3-ph-pins { pins = "PH4\0PH5"; function = "i2c3"; phandle = <0x47>; }; i2c4-ph-pins { pins = "PH6\0PH7"; function = "i2c4"; phandle = <0x48>; }; i2c3-pg-pins { pins = "PG17\0PG18"; function = "i2c3"; phandle = <0x49>; }; i2c4-pg-pins { pins = "PG15\0PG16"; function = "i2c4"; phandle = <0x4a>; }; ir-rx-pin { pins = "PH10"; function = "ir_rx"; phandle = <0x34>; }; mmc0-pins { pins = "PF0\0PF1\0PF2\0PF3\0PF4\0PF5"; function = "mmc0"; drive-strength = <0x1e>; bias-pull-up; phandle = <0x13>; }; mmc1-pins { pins = "PG0\0PG1\0PG2\0PG3\0PG4\0PG5"; function = "mmc1"; drive-strength = <0x1e>; bias-pull-up; phandle = <0x15>; }; mmc2-pins { pins = "PC0\0PC1\0PC5\0PC6\0PC8\0PC9\0PC10\0PC11\0PC13\0PC14\0PC15\0PC16"; function = "mmc2"; drive-strength = <0x1e>; bias-pull-up; phandle = <0x17>; }; rmii-pins { pins = "PA0\0PA1\0PA2\0PA3\0PA4\0PA5\0PA6\0PA7\0PA8\0PA9"; function = "emac1"; drive-strength = <0x28>; phandle = <0x26>; }; spi0-pins { pins = "PC0\0PC2\0PC4"; function = "spi0"; phandle = <0x21>; }; spi0-cs0-pin { pins = "PC3"; function = "spi0"; phandle = <0x4b>; }; spi1-pins { pins = "PH6\0PH7\0PH8"; function = "spi1"; phandle = <0x22>; }; spi1-cs0-pin { pins = "PH5"; function = "spi1"; phandle = <0x4c>; }; spi1-cs1-pin { pins = "PH9"; function = "spi1"; phandle = <0x4d>; }; spdif-tx-pin { pins = "PH4"; function = "spdif"; phandle = <0x24>; }; uart0-ph-pins { pins = "PH0\0PH1"; function = "uart0"; phandle = <0x1d>; }; uart2-pins { pins = "PH5\0PH6"; function = "uart2"; phandle = <0x4e>; }; uart2-rts-cts-pins { pins = "PH7\0PH8"; function = "uart2"; phandle = <0x4f>; }; uart5-pins { pins = "PH2\0PH3"; function = "uart5"; phandle = <0x50>; }; uart1-pins { pins = "PG6\0PG7"; function = "uart1"; phandle = <0x1e>; }; uart1-rts-cts-pins { pins = "PG8\0PG9"; function = "uart1"; phandle = <0x1f>; }; x32clk-fanout-pin { pins = "PG10"; function = "clock"; phandle = <0x3a>; }; }; interrupt-controller@3021000 { compatible = "arm,gic-400"; reg = <0x3021000 0x1000 0x3022000 0x2000 0x3024000 0x2000 0x3026000 0x2000>; interrupts = <0x01 0x09 0xf04>; interrupt-controller; #interrupt-cells = <0x03>; phandle = <0x01>; }; iommu@30f0000 { compatible = "allwinner,sun50i-h616-iommu\0allwinner,sun50i-h6-iommu"; reg = <0x30f0000 0x10000>; interrupts = <0x00 0x3d 0x04>; clocks = <0x02 0x30>; resets = <0x02 0x0b>; #iommu-cells = <0x01>; status = "okay"; phandle = <0x51>; }; mmc@4020000 { compatible = "allwinner,sun50i-h616-mmc\0allwinner,sun50i-a100-mmc"; reg = <0x4020000 0x1000>; clocks = <0x02 0x3f 0x02 0x3c>; clock-names = "ahb\0mmc"; resets = <0x02 0x0e>; reset-names = "ahb"; interrupts = <0x00 0x23 0x04>; pinctrl-names = "default"; pinctrl-0 = <0x13>; status = "okay"; max-frequency = <0x8f0d180>; cap-sd-highspeed; cap-mmc-highspeed; mmc-ddr-3_3v; cap-sdio-irq; #address-cells = <0x01>; #size-cells = <0x00>; vmmc-supply = <0x12>; cd-gpios = <0x14 0x08 0x10 0x01>; bus-width = <0x04>; phandle = <0x52>; }; mmc@4021000 { compatible = "allwinner,sun50i-h616-mmc\0allwinner,sun50i-a100-mmc"; reg = <0x4021000 0x1000>; clocks = <0x02 0x40 0x02 0x3d>; clock-names = "ahb\0mmc"; resets = <0x02 0x0f>; reset-names = "ahb"; interrupts = <0x00 0x24 0x04>; pinctrl-names = "default"; pinctrl-0 = <0x15>; status = "okay"; max-frequency = <0x8f0d180>; cap-sd-highspeed; cap-mmc-highspeed; mmc-ddr-3_3v; cap-sdio-irq; #address-cells = <0x01>; #size-cells = <0x00>; vmmc-supply = <0x12>; vqmmc-supply = <0x11>; mmc-pwrseq = <0x16>; bus-width = <0x04>; non-removable; phandle = <0x53>; wifi@1 { reg = <0x01>; phandle = <0x54>; }; }; mmc@4022000 { compatible = "allwinner,sun50i-h616-emmc\0allwinner,sun50i-a100-emmc"; reg = <0x4022000 0x1000>; clocks = <0x02 0x41 0x02 0x3e>; clock-names = "ahb\0mmc"; resets = <0x02 0x10>; reset-names = "ahb"; interrupts = <0x00 0x25 0x04>; pinctrl-names = "default"; pinctrl-0 = <0x17>; status = "okay"; max-frequency = <0x8f0d180>; cap-sd-highspeed; cap-mmc-highspeed; mmc-ddr-3_3v; cap-sdio-irq; #address-cells = <0x01>; #size-cells = <0x00>; vmmc-supply = <0x12>; vqmmc-supply = <0x11>; bus-width = <0x08>; non-removable; cap-mmc-hw-reset; mmc-ddr-1_8v; mmc-hs200-1_8v; phandle = <0x55>; }; codec@05096000 { #sound-dai-cells = <0x00>; compatible = "allwinner,sun50i-h616-codec"; reg = <0x5096000 0x31c>; interrupts = <0x00 0x3a 0x04>; clocks = <0x02 0x5d 0x02 0x5b 0x02 0x5c>; clock-names = "apb\0audio-codec-1x\0audio-codec-4x"; resets = <0x02 0x24>; dmas = <0x18 0x06>; dma-names = "tx"; status = "okay"; allwinner,audio-routing = "Line Out\0LINEOUT"; phandle = <0x56>; }; ahub_dam_plat@5097000 { #sound-dai-cells = <0x00>; compatible = "allwinner,sunxi-snd-plat-ahub_dam"; reg = <0x5097000 0x1000>; resets = <0x02 0x25>; clocks = <0x02 0x5b 0x02 0x5c 0x02 0x5e 0x02 0x5f>; clock-names = "clk_pll_audio\0clk_pll_audio_4x\0clk_audio_hub\0clk_bus_audio_hub"; status = "okay"; phandle = <0x19>; }; ahub_dam_mach { compatible = "allwinner,sunxi-snd-mach"; soundcard-mach,name = "ahubdam"; status = "okay"; phandle = <0x57>; soundcard-mach,cpu { sound-dai = <0x19>; }; soundcard-mach,codec { }; }; ahub1_plat { #sound-dai-cells = <0x00>; compatible = "allwinner,sunxi-snd-plat-ahub"; apb_num = <0x01>; dmas = <0x18 0x04 0x18 0x04>; dma-names = "tx\0rx"; playback_cma = <0x80>; capture_cma = <0x80>; tx_fifo_size = <0x80>; rx_fifo_size = <0x80>; tdm_num = <0x01>; tx_pin = <0x00>; rx_pin = <0x00>; status = "okay"; phandle = <0x1b>; }; ahub1_mach { compatible = "allwinner,sunxi-snd-mach"; soundcard-mach,name = "HDMI"; soundcard-mach,format = "i2s"; soundcard-mach,frame-master = <0x1a>; soundcard-mach,bitclock-master = <0x1a>; soundcard-mach,slot-num = <0x02>; soundcard-mach,slot-width = <0x20>; status = "okay"; phandle = <0x58>; soundcard-mach,cpu { sound-dai = <0x1b>; soundcard-mach,pll-fs = <0x04>; soundcard-mach,mclk-fs = <0x00>; phandle = <0x1a>; }; soundcard-mach,codec { sound-dai = <0x1c>; phandle = <0x59>; }; }; serial@5000000 { compatible = "snps,dw-apb-uart"; reg = <0x5000000 0x400>; interrupts = <0x00 0x00 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x42>; dmas = <0x18 0x0e 0x18 0x0e>; dma-names = "tx\0rx"; resets = <0x02 0x11>; status = "okay"; pinctrl-names = "default"; pinctrl-0 = <0x1d>; phandle = <0x5a>; }; serial@5000400 { compatible = "snps,dw-apb-uart"; reg = <0x5000400 0x400>; interrupts = <0x00 0x01 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x43>; dmas = <0x18 0x0f 0x18 0x0f>; dma-names = "tx\0rx"; resets = <0x02 0x12>; status = "okay"; pinctrl-names = "default"; pinctrl-0 = <0x1e 0x1f>; uart-has-rtscts; phandle = <0x5b>; bluetooth { compatible = "brcm,bcm43438-bt"; shutdown-gpios = <0x14 0x06 0x13 0x00>; clocks = <0x10 0x01>; host-wakeup-gpios = <0x14 0x06 0x10 0x00>; clock-names = "lpo"; vddio-supply = <0x12>; device-wakeup-gpios = <0x14 0x06 0x11 0x00>; vbat-supply = <0x12>; }; }; serial@5000800 { compatible = "snps,dw-apb-uart"; reg = <0x5000800 0x400>; interrupts = <0x00 0x02 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x44>; dmas = <0x18 0x10 0x18 0x10>; dma-names = "tx\0rx"; resets = <0x02 0x13>; status = "disabled"; phandle = <0x5c>; }; serial@5000c00 { compatible = "snps,dw-apb-uart"; reg = <0x5000c00 0x400>; interrupts = <0x00 0x03 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x45>; dmas = <0x18 0x11 0x18 0x11>; dma-names = "tx\0rx"; resets = <0x02 0x14>; status = "disabled"; phandle = <0x5d>; }; serial@5001000 { compatible = "snps,dw-apb-uart"; reg = <0x5001000 0x400>; interrupts = <0x00 0x04 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x46>; dmas = <0x18 0x12 0x18 0x12>; dma-names = "tx\0rx"; resets = <0x02 0x15>; status = "disabled"; phandle = <0x5e>; }; serial@5001400 { compatible = "snps,dw-apb-uart"; reg = <0x5001400 0x400>; interrupts = <0x00 0x05 0x04>; reg-shift = <0x02>; reg-io-width = <0x04>; clocks = <0x02 0x47>; dmas = <0x18 0x13 0x18 0x13>; dma-names = "tx\0rx"; resets = <0x02 0x16>; status = "disabled"; phandle = <0x5f>; }; i2c@5002000 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x5002000 0x400>; interrupts = <0x00 0x06 0x04>; clocks = <0x02 0x48>; dmas = <0x18 0x2b 0x18 0x2b>; dma-names = "rx\0tx"; resets = <0x02 0x17>; pinctrl-names = "default"; pinctrl-0 = <0x20>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x60>; }; i2c@5002400 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x5002400 0x400>; interrupts = <0x00 0x07 0x04>; clocks = <0x02 0x49>; dmas = <0x18 0x2c 0x18 0x2c>; dma-names = "rx\0tx"; resets = <0x02 0x18>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x61>; }; i2c@5002800 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x5002800 0x400>; interrupts = <0x00 0x08 0x04>; clocks = <0x02 0x4a>; dmas = <0x18 0x2d 0x18 0x2d>; dma-names = "rx\0tx"; resets = <0x02 0x19>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x62>; }; i2c@5002c00 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x5002c00 0x400>; interrupts = <0x00 0x09 0x04>; clocks = <0x02 0x4b>; dmas = <0x18 0x2e 0x18 0x2e>; dma-names = "rx\0tx"; resets = <0x02 0x1a>; status = "okay"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x63>; }; i2c@5003000 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x5003000 0x400>; interrupts = <0x00 0x0a 0x04>; clocks = <0x02 0x4c>; dmas = <0x18 0x2f 0x18 0x2f>; dma-names = "rx\0tx"; resets = <0x02 0x1b>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x64>; }; spi@5010000 { compatible = "allwinner,sun50i-h616-spi\0allwinner,sun8i-h3-spi"; reg = <0x5010000 0x1000>; interrupts = <0x00 0x0c 0x04>; clocks = <0x02 0x4f 0x02 0x4d>; clock-names = "ahb\0mod"; dmas = <0x18 0x16 0x18 0x16>; dma-names = "rx\0tx"; resets = <0x02 0x1c>; pinctrl-names = "default"; pinctrl-0 = <0x21>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x65>; }; spi@5011000 { compatible = "allwinner,sun50i-h616-spi\0allwinner,sun8i-h3-spi"; reg = <0x5011000 0x1000>; interrupts = <0x00 0x0d 0x04>; clocks = <0x02 0x50 0x02 0x4e>; clock-names = "ahb\0mod"; dmas = <0x18 0x17 0x18 0x17>; dma-names = "rx\0tx"; resets = <0x02 0x1d>; pinctrl-names = "default"; pinctrl-0 = <0x22>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x66>; }; ethernet@5020000 { compatible = "allwinner,sun50i-h616-emac0\0allwinner,sun50i-a64-emac"; reg = <0x5020000 0x10000>; interrupts = <0x00 0x0e 0x04>; interrupt-names = "macirq"; clocks = <0x02 0x52>; clock-names = "stmmaceth"; resets = <0x02 0x1e>; reset-names = "stmmaceth"; syscon = <0x23>; status = "disabled"; phandle = <0x67>; mdio { compatible = "snps,dwmac-mdio"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x68>; }; }; spdif@5093000 { compatible = "allwinner,sun50i-h616-spdif"; reg = <0x5093000 0x400>; interrupts = <0x00 0x15 0x04>; clocks = <0x02 0x58 0x02 0x57>; clock-names = "apb\0spdif"; resets = <0x02 0x22>; dmas = <0x18 0x02>; dma-names = "tx"; pinctrl-names = "default"; pinctrl-0 = <0x24>; #sound-dai-cells = <0x00>; status = "disabled"; phandle = <0x69>; }; thermal-sensor@5070400 { compatible = "allwinner,sun50i-h616-ths"; reg = <0x5070400 0x400>; interrupts = <0x00 0x13 0x04>; clocks = <0x02 0x56>; clock-names = "bus"; resets = <0x02 0x21>; nvmem-cells = <0x25>; nvmem-cell-names = "calibration"; allwinner,sram = <0x23>; #thermal-sensor-cells = <0x01>; phandle = <0x37>; }; ethernet@5030000 { compatible = "allwinner,sun50i-h616-emac"; syscon = <0x23 0x01>; reg = <0x5030000 0x10000>; interrupts = <0x00 0x0f 0x04>; interrupt-names = "macirq"; resets = <0x02 0x1f>; reset-names = "stmmaceth"; clocks = <0x02 0x53>; clock-names = "stmmaceth"; status = "okay"; pinctrl-names = "default"; pinctrl-0 = <0x26>; phy-mode = "rmii"; phy-handle = <0x27>; phy-supply = <0x11>; allwinner,rx-delay-ps = <0xc1c>; allwinner,tx-delay-ps = <0x2bc>; phandle = <0x6a>; mdio { compatible = "snps,dwmac-mdio"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x6b>; ethernet-phy@0 { compatible = "ethernet-phy-ieee802.3-c22"; reg = <0x00>; phandle = <0x27>; }; }; }; usb@5100000 { compatible = "allwinner,sun50i-h616-musb\0allwinner,sun8i-h3-musb"; reg = <0x5100000 0x400>; clocks = <0x02 0x70>; resets = <0x02 0x32>; interrupts = <0x00 0x19 0x04>; interrupt-names = "mc"; phys = <0x28 0x00>; phy-names = "usb"; extcon = <0x28 0x00>; status = "okay"; dr_mode = "host"; phandle = <0x6c>; }; phy@5100400 { compatible = "allwinner,sun50i-h616-usb-phy"; reg = <0x5100400 0x24 0x5101800 0x14 0x5200800 0x14 0x5310800 0x14 0x5311800 0x14>; reg-names = "phy_ctrl\0pmu0\0pmu1\0pmu2\0pmu3"; clocks = <0x02 0x61 0x02 0x63 0x02 0x65 0x02 0x67 0x02 0x6e>; clock-names = "usb0_phy\0usb1_phy\0usb2_phy\0usb3_phy\0pmu2_clk"; resets = <0x02 0x26 0x02 0x27 0x02 0x28 0x02 0x29>; reset-names = "usb0_reset\0usb1_reset\0usb2_reset\0usb3_reset"; status = "okay"; #phy-cells = <0x01>; phandle = <0x28>; }; usb@5101000 { compatible = "allwinner,sun50i-h616-ehci\0generic-ehci"; reg = <0x5101000 0x100>; interrupts = <0x00 0x1a 0x04>; clocks = <0x02 0x68 0x02 0x6c 0x02 0x60>; resets = <0x02 0x2a 0x02 0x2e>; phys = <0x28 0x00>; phy-names = "usb"; status = "okay"; phandle = <0x6d>; }; usb@5101400 { compatible = "allwinner,sun50i-h616-ohci\0generic-ohci"; reg = <0x5101400 0x100>; interrupts = <0x00 0x1b 0x04>; clocks = <0x02 0x68 0x02 0x60>; resets = <0x02 0x2a>; phys = <0x28 0x00>; phy-names = "usb"; status = "okay"; phandle = <0x6e>; }; usb@5200000 { compatible = "allwinner,sun50i-h616-ehci\0generic-ehci"; reg = <0x5200000 0x100>; interrupts = <0x00 0x1c 0x04>; clocks = <0x02 0x69 0x02 0x6d 0x02 0x62>; resets = <0x02 0x2b 0x02 0x2f>; phys = <0x28 0x01>; phy-names = "usb"; status = "okay"; phandle = <0x6f>; }; usb@5200400 { compatible = "allwinner,sun50i-h616-ohci\0generic-ohci"; reg = <0x5200400 0x100>; interrupts = <0x00 0x1d 0x04>; clocks = <0x02 0x69 0x02 0x62>; resets = <0x02 0x2b>; phys = <0x28 0x01>; phy-names = "usb"; status = "okay"; phandle = <0x70>; }; usb@5310000 { compatible = "allwinner,sun50i-h616-ehci\0generic-ehci"; reg = <0x5310000 0x100>; interrupts = <0x00 0x1e 0x04>; clocks = <0x02 0x6a 0x02 0x6e 0x02 0x64>; resets = <0x02 0x2c 0x02 0x30>; phys = <0x28 0x02>; phy-names = "usb"; status = "disabled"; phandle = <0x71>; }; usb@5310400 { compatible = "allwinner,sun50i-h616-ohci\0generic-ohci"; reg = <0x5310400 0x100>; interrupts = <0x00 0x1f 0x04>; clocks = <0x02 0x6a 0x02 0x64>; resets = <0x02 0x2c>; phys = <0x28 0x02>; phy-names = "usb"; status = "disabled"; phandle = <0x72>; }; usb@5311000 { compatible = "allwinner,sun50i-h616-ehci\0generic-ehci"; reg = <0x5311000 0x100>; interrupts = <0x00 0x20 0x04>; clocks = <0x02 0x6b 0x02 0x6f 0x02 0x66>; resets = <0x02 0x2d 0x02 0x31>; phys = <0x28 0x03>; phy-names = "usb"; status = "disabled"; phandle = <0x73>; }; usb@5311400 { compatible = "allwinner,sun50i-h616-ohci\0generic-ohci"; reg = <0x5311400 0x100>; interrupts = <0x00 0x21 0x04>; clocks = <0x02 0x6b 0x02 0x66>; resets = <0x02 0x2d>; phys = <0x28 0x03>; phy-names = "usb"; status = "disabled"; phandle = <0x74>; }; hdmi@6000000 { #sound-dai-cells = <0x00>; compatible = "allwinner,sun50i-h616-dw-hdmi\0allwinner,sun50i-h6-dw-hdmi"; reg = <0x6000000 0x10000>; reg-io-width = <0x01>; interrupts = <0x00 0x3f 0x04>; clocks = <0x02 0x75 0x02 0x73 0x02 0x72 0x02 0x74 0x02 0x7e 0x02 0x7f>; clock-names = "iahb\0isfr\0tmds\0cec\0hdcp\0hdcp-bus"; resets = <0x02 0x33 0x02 0x3a>; reset-names = "ctrl\0hdcp"; phys = <0x29>; phy-names = "phy"; status = "okay"; phandle = <0x1c>; ports { #address-cells = <0x01>; #size-cells = <0x00>; port@0 { reg = <0x00>; phandle = <0x75>; endpoint { remote-endpoint = <0x2a>; phandle = <0x2f>; }; }; port@1 { reg = <0x01>; phandle = <0x76>; endpoint { remote-endpoint = <0x2b>; phandle = <0x39>; }; }; }; }; hdmi-phy@6010000 { compatible = "allwinner,sun50i-h616-hdmi-phy"; reg = <0x6010000 0x10000>; clocks = <0x02 0x75 0x02 0x73>; clock-names = "bus\0mod"; resets = <0x02 0x34>; reset-names = "phy"; #phy-cells = <0x00>; phandle = <0x29>; }; tcon-top@6510000 { compatible = "allwinner,sun50i-h6-tcon-top"; reg = <0x6510000 0x1000>; clocks = <0x02 0x76 0x02 0x77>; clock-names = "bus\0tcon-tv0"; clock-output-names = "tcon-top-tv0"; resets = <0x02 0x35>; #clock-cells = <0x01>; phandle = <0x30>; ports { #address-cells = <0x01>; #size-cells = <0x00>; port@0 { #address-cells = <0x01>; #size-cells = <0x00>; reg = <0x00>; phandle = <0x77>; endpoint@0 { reg = <0x00>; remote-endpoint = <0x2c>; phandle = <0x0c>; }; }; port@1 { #address-cells = <0x01>; #size-cells = <0x00>; reg = <0x01>; phandle = <0x78>; endpoint@2 { reg = <0x02>; remote-endpoint = <0x2d>; phandle = <0x31>; }; }; port@4 { #address-cells = <0x01>; #size-cells = <0x00>; reg = <0x04>; phandle = <0x79>; endpoint@0 { reg = <0x00>; remote-endpoint = <0x2e>; phandle = <0x32>; }; }; port@5 { reg = <0x05>; phandle = <0x7a>; endpoint { remote-endpoint = <0x2f>; phandle = <0x2a>; }; }; }; }; lcd-controller@6515000 { compatible = "allwinner,sun50i-h6-tcon-tv\0allwinner,sun8i-r40-tcon-tv"; reg = <0x6515000 0x1000>; interrupts = <0x00 0x42 0x04>; clocks = <0x02 0x79 0x30 0x00>; clock-names = "ahb\0tcon-ch1"; resets = <0x02 0x36>; reset-names = "lcd"; phandle = <0x7b>; ports { #address-cells = <0x01>; #size-cells = <0x00>; port@0 { reg = <0x00>; phandle = <0x7c>; endpoint { remote-endpoint = <0x31>; phandle = <0x2d>; }; }; port@1 { #address-cells = <0x01>; #size-cells = <0x00>; reg = <0x01>; phandle = <0x7d>; endpoint@1 { reg = <0x01>; remote-endpoint = <0x32>; phandle = <0x2e>; }; }; }; }; rtc@7000000 { compatible = "allwinner,sun50i-h616-rtc"; reg = <0x7000000 0x400>; interrupts = <0x00 0x68 0x04>; clocks = <0x33 0x0e 0x0f 0x02 0x80>; clock-names = "bus\0hosc\0pll-32k"; #clock-cells = <0x01>; phandle = <0x10>; }; clock@7010000 { compatible = "allwinner,sun50i-h616-r-ccu"; reg = <0x7010000 0x210>; clocks = <0x0f 0x10 0x00 0x10 0x02 0x02 0x04>; clock-names = "hosc\0losc\0iosc\0pll-periph"; #clock-cells = <0x01>; #reset-cells = <0x01>; phandle = <0x33>; }; interrupt-controller@7010320 { compatible = "allwinner,sun50i-h616-nmi\0allwinner,sun9i-a80-nmi"; reg = <0x7010320 0x0c>; interrupt-controller; #interrupt-cells = <0x02>; interrupts = <0x00 0x67 0x04>; phandle = <0x7e>; }; pinctrl@7022000 { compatible = "allwinner,sun50i-h616-r-pinctrl"; reg = <0x7022000 0x400>; interrupts = <0x00 0x8f 0x04>; clocks = <0x33 0x02 0x0f 0x10 0x00>; clock-names = "apb\0hosc\0losc"; gpio-controller; #gpio-cells = <0x03>; interrupt-controller; #interrupt-cells = <0x03>; phandle = <0x7f>; r-i2c-pins { pins = "PL0\0PL1"; function = "s_i2c"; phandle = <0x80>; }; r-rsb-pins { pins = "PL0\0PL1"; function = "s_rsb"; phandle = <0x36>; }; }; ir@7040000 { compatible = "allwinner,sun50i-h616-ir\0allwinner,sun6i-a31-ir"; reg = <0x7040000 0x400>; interrupts = <0x00 0x6a 0x04>; clocks = <0x33 0x09 0x33 0x0b>; clock-names = "apb\0ir"; resets = <0x33 0x05>; pinctrl-names = "default"; pinctrl-0 = <0x34>; status = "okay"; phandle = <0x81>; }; i2c@7081400 { compatible = "allwinner,sun50i-h616-i2c\0allwinner,sun8i-v536-i2c\0allwinner,sun6i-a31-i2c"; reg = <0x7081400 0x400>; interrupts = <0x00 0x69 0x04>; clocks = <0x33 0x08>; dmas = <0x18 0x30 0x18 0x30>; dma-names = "rx\0tx"; resets = <0x33 0x04>; status = "okay"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x82>; pmic@36 { compatible = "x-powers,axp313a"; reg = <0x36>; #interrupt-cells = <0x01>; interrupt-controller; vin1-supply = <0x35>; vin2-supply = <0x35>; vin3-supply = <0x35>; phandle = <0x83>; regulators { aldo1 { regulator-always-on; regulator-min-microvolt = <0x1b7740>; regulator-max-microvolt = <0x1b7740>; regulator-name = "vcc-1v8-pll"; phandle = <0x11>; }; dldo1 { regulator-always-on; regulator-min-microvolt = <0x325aa0>; regulator-max-microvolt = <0x325aa0>; regulator-name = "vcc-3v3-io-mmc"; phandle = <0x12>; }; dcdc1 { regulator-always-on; regulator-min-microvolt = <0xc5c10>; regulator-max-microvolt = <0xf1b30>; regulator-name = "vdd-gpu-sys"; phandle = <0x0d>; }; dcdc2 { regulator-always-on; regulator-min-microvolt = <0xc5c10>; regulator-max-microvolt = <0x10c8e0>; regulator-name = "vdd-cpu"; phandle = <0x04>; }; dcdc3 { regulator-always-on; regulator-min-microvolt = <0x14c080>; regulator-max-microvolt = <0x14c080>; regulator-name = "vdd-dram"; phandle = <0x84>; }; }; }; }; rsb@7083000 { compatible = "allwinner,sun50i-h616-rsb\0allwinner,sun8i-a23-rsb"; reg = <0x7083000 0x400>; interrupts = <0x00 0x6d 0x04>; clocks = <0x33 0x0d>; clock-frequency = <0x2dc6c0>; resets = <0x33 0x07>; pinctrl-names = "default"; pinctrl-0 = <0x36>; status = "disabled"; #address-cells = <0x01>; #size-cells = <0x00>; phandle = <0x85>; }; dump_reg@20000 { compatible = "allwinner,sunxi-dump-reg"; reg = <0x00 0x3001000 0x00 0xf20>; status = "okay"; phandle = <0x86>; }; sunxi-info { compatible = "allwinner,sun50i-h616-sys-info"; status = "okay"; }; addr-mgt { compatible = "allwinner,sunxi-addr_mgt"; type_addr_wifi = <0x02>; type_addr_bt = <0x02>; type_addr_eth = <0x02>; status = "okay"; phandle = <0x87>; }; }; thermal-zones { cpu-thermal { polling-delay-passive = <0x1f4>; polling-delay = <0x3e8>; thermal-sensors = <0x37 0x02>; sustainable-power = <0x3e8>; trips { cpu-trip-0 { temperature = <0xea60>; type = "passive"; hysteresis = <0x00>; phandle = <0x88>; }; cpu-trip-1 { temperature = <0x11170>; type = "passive"; hysteresis = <0x00>; phandle = <0x89>; }; cpu-trip-2 { temperature = <0x1adb0>; type = "critical"; hysteresis = <0x00>; phandle = <0x8a>; }; }; }; gpu-thermal { polling-delay-passive = <0x1f4>; polling-delay = <0x3e8>; thermal-sensors = <0x37 0x00>; sustainable-power = <0x44c>; trips { gpu-trip-0 { temperature = <0x1adb0>; type = "critical"; hysteresis = <0x00>; phandle = <0x8b>; }; }; }; ve-thermal { polling-delay-passive = <0x00>; polling-delay = <0x00>; thermal-sensors = <0x37 0x01>; trips { ve-trip-0 { temperature = <0x1adb0>; type = "critical"; hysteresis = <0x00>; phandle = <0x8c>; }; }; }; ddr-thermal { polling-delay-passive = <0x00>; polling-delay = <0x00>; thermal-sensors = <0x37 0x03>; trips { ddr-trip-0 { temperature = <0x1adb0>; type = "critical"; hysteresis = <0x00>; phandle = <0x8d>; }; }; }; }; opp-table-cpu { compatible = "allwinner,sun50i-h616-operating-points"; nvmem-cells = <0x38>; opp-shared; phandle = <0x03>; opp-480000000 { opp-hz = <0x00 0x1c9c3800>; opp-microvolt = <0xdbba0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x1f>; }; opp-600000000 { opp-hz = <0x00 0x23c34600>; opp-microvolt = <0xdbba0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x12>; }; opp-720000000 { opp-hz = <0x00 0x2aea5400>; opp-microvolt = <0xdbba0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x0d>; }; opp-792000000 { opp-hz = <0x00 0x2f34f600>; opp-microvolt-speed1 = <0xdbba0>; opp-microvolt-speed4 = <0xe57e0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x12>; }; opp-936000000 { opp-hz = <0x00 0x37ca3a00>; opp-microvolt = <0xdbba0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x0d>; }; opp-1008000000 { opp-hz = <0x00 0x3c14dc00>; opp-microvolt-speed0 = <0xe7ef0>; opp-microvolt-speed1 = <0xe57e0>; opp-microvolt-speed2 = <0xe7ef0>; opp-microvolt-speed3 = <0xe7ef0>; opp-microvolt-speed4 = <0xf9060>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x1f>; }; opp-1104000000 { opp-hz = <0x00 0x41cdb400>; opp-microvolt-speed0 = <0xf4240>; opp-microvolt-speed2 = <0xf4240>; opp-microvolt-speed3 = <0xf4240>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x0d>; }; opp-1200000000 { opp-hz = <0x00 0x47868c00>; opp-microvolt-speed0 = <0x100590>; opp-microvolt-speed1 = <0xf9060>; opp-microvolt-speed2 = <0x100590>; opp-microvolt-speed3 = <0x100590>; opp-microvolt-speed4 = <0x10c8e0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x1f>; }; opp-1320000000 { opp-hz = <0x00 0x4ead9a00>; opp-microvolt = <0x10c8e0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x1d>; }; opp-1416000000 { opp-hz = <0x00 0x54667200>; opp-microvolt = <0x10c8e0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x0d>; }; opp-1512000000 { opp-hz = <0x00 0x5a1f4a00>; opp-microvolt-speed1 = <0x10c8e0>; opp-microvolt-speed3 = <0x10c8e0>; clock-latency-ns = <0x3b9b0>; opp-supported-hw = <0x0a>; }; }; aliases { ethernet0 = "/soc/ethernet@5030000"; ethernet1 = "/soc/mmc@4021000/wifi@1"; serial0 = "/soc/serial@5000000"; }; chosen { stdout-path = "serial0:115200n8"; }; connector { compatible = "hdmi-connector"; type = "a"; port { endpoint { remote-endpoint = <0x39>; phandle = <0x2b>; }; }; }; vcc5v { compatible = "regulator-fixed"; regulator-name = "vcc-5v"; regulator-min-microvolt = <0x4c4b40>; regulator-max-microvolt = <0x4c4b40>; regulator-always-on; phandle = <0x35>; }; vcc3v3 { compatible = "regulator-fixed"; regulator-name = "vcc-3v3"; regulator-min-microvolt = <0x325aa0>; regulator-max-microvolt = <0x325aa0>; regulator-always-on; phandle = <0x8e>; }; pwrseq { compatible = "mmc-pwrseq-simple"; clocks = <0x10 0x01>; clock-names = "ext_clock"; pinctrl-0 = <0x3a>; pinctrl-names = "default"; reset-gpios = <0x14 0x06 0x12 0x01>; phandle = <0x16>; }; __symbols__ { cpu0 = "/cpus/cpu@0"; cpu1 = "/cpus/cpu@1"; cpu2 = "/cpus/cpu@2"; cpu3 = "/cpus/cpu@3"; de = "/display-engine"; osc24M = "/osc24M-clk"; display_clocks = "/soc/bus@1000000/clock@8000"; mixer0 = "/soc/bus@1000000/mixer@100000"; mixer0_out = "/soc/bus@1000000/mixer@100000/ports/port@1"; mixer0_out_tcon_top_mixer0 = "/soc/bus@1000000/mixer@100000/ports/port@1/endpoint"; gpu = "/soc/gpu@1800000"; deinterlace = "/soc/deinterlace@1420000"; syscon = "/soc/syscon@3000000"; sram_a2 = "/soc/syscon@3000000/sram@100000"; scpi_sram = "/soc/syscon@3000000/sram@100000/scpi-sram@17c00"; sram_c = "/soc/syscon@3000000/sram@28000"; de3_sram = "/soc/syscon@3000000/sram@28000/sram-section@0"; sram_c1 = "/soc/syscon@3000000/sram@1a00000"; ve_sram = "/soc/syscon@3000000/sram@1a00000/sram-section@0"; ccu = "/soc/clock@3001000"; dma = "/soc/dma-controller@3002000"; sid = "/soc/efuse@3006000"; ths_calibration = "/soc/efuse@3006000/thermal-sensor-calibration@14"; cpu_speed_grade = "/soc/efuse@3006000/cpu-speed-grade@0"; watchdog = "/soc/watchdog@30090a0"; pio = "/soc/pinctrl@300b000"; ext_rgmii_pins = "/soc/pinctrl@300b000/rgmii-pins"; i2c0_pins = "/soc/pinctrl@300b000/i2c0-pins"; i2c2_ph_pins = "/soc/pinctrl@300b000/i2c2-ph-pins"; i2c3_ph_pins = "/soc/pinctrl@300b000/i2c3-ph-pins"; i2c4_ph_pins = "/soc/pinctrl@300b000/i2c4-ph-pins"; i2c3_pg_pins = "/soc/pinctrl@300b000/i2c3-pg-pins"; i2c4_pg_pins = "/soc/pinctrl@300b000/i2c4-pg-pins"; ir_rx_pin = "/soc/pinctrl@300b000/ir-rx-pin"; mmc0_pins = "/soc/pinctrl@300b000/mmc0-pins"; mmc1_pins = "/soc/pinctrl@300b000/mmc1-pins"; mmc2_pins = "/soc/pinctrl@300b000/mmc2-pins"; rmii_pins = "/soc/pinctrl@300b000/rmii-pins"; spi0_pins = "/soc/pinctrl@300b000/spi0-pins"; spi0_cs0_pin = "/soc/pinctrl@300b000/spi0-cs0-pin"; spi1_pins = "/soc/pinctrl@300b000/spi1-pins"; spi1_cs0_pin = "/soc/pinctrl@300b000/spi1-cs0-pin"; spi1_cs1_pin = "/soc/pinctrl@300b000/spi1-cs1-pin"; spdif_tx_pin = "/soc/pinctrl@300b000/spdif-tx-pin"; uart0_ph_pins = "/soc/pinctrl@300b000/uart0-ph-pins"; uart2_pins = "/soc/pinctrl@300b000/uart2-pins"; uart2_rts_cts_pins = "/soc/pinctrl@300b000/uart2-rts-cts-pins"; uart5_pins = "/soc/pinctrl@300b000/uart5-pins"; uart1_pins = "/soc/pinctrl@300b000/uart1-pins"; uart1_rts_cts_pins = "/soc/pinctrl@300b000/uart1-rts-cts-pins"; x32clk_fanout_pin = "/soc/pinctrl@300b000/x32clk-fanout-pin"; gic = "/soc/interrupt-controller@3021000"; iommu = "/soc/iommu@30f0000"; mmc0 = "/soc/mmc@4020000"; mmc1 = "/soc/mmc@4021000"; sdio_wifi = "/soc/mmc@4021000/wifi@1"; mmc2 = "/soc/mmc@4022000"; codec = "/soc/codec@05096000"; ahub_dam_plat = "/soc/ahub_dam_plat@5097000"; ahub_dam_mach = "/soc/ahub_dam_mach"; ahub1_plat = "/soc/ahub1_plat"; ahub1_mach = "/soc/ahub1_mach"; ahub1_cpu = "/soc/ahub1_mach/soundcard-mach,cpu"; ahub1_codec = "/soc/ahub1_mach/soundcard-mach,codec"; uart0 = "/soc/serial@5000000"; uart1 = "/soc/serial@5000400"; uart2 = "/soc/serial@5000800"; uart3 = "/soc/serial@5000c00"; uart4 = "/soc/serial@5001000"; uart5 = "/soc/serial@5001400"; i2c0 = "/soc/i2c@5002000"; i2c1 = "/soc/i2c@5002400"; i2c2 = "/soc/i2c@5002800"; i2c3 = "/soc/i2c@5002c00"; i2c4 = "/soc/i2c@5003000"; spi0 = "/soc/spi@5010000"; spi1 = "/soc/spi@5011000"; emac0 = "/soc/ethernet@5020000"; mdio0 = "/soc/ethernet@5020000/mdio"; spdif = "/soc/spdif@5093000"; ths = "/soc/thermal-sensor@5070400"; emac1 = "/soc/ethernet@5030000"; mdio1 = "/soc/ethernet@5030000/mdio"; rmii_phy = "/soc/ethernet@5030000/mdio/ethernet-phy@0"; usbotg = "/soc/usb@5100000"; usbphy = "/soc/phy@5100400"; ehci0 = "/soc/usb@5101000"; ohci0 = "/soc/usb@5101400"; ehci1 = "/soc/usb@5200000"; ohci1 = "/soc/usb@5200400"; ehci2 = "/soc/usb@5310000"; ohci2 = "/soc/usb@5310400"; ehci3 = "/soc/usb@5311000"; ohci3 = "/soc/usb@5311400"; hdmi = "/soc/hdmi@6000000"; hdmi_in = "/soc/hdmi@6000000/ports/port@0"; hdmi_in_tcon_top = "/soc/hdmi@6000000/ports/port@0/endpoint"; hdmi_out = "/soc/hdmi@6000000/ports/port@1"; hdmi_out_con = "/soc/hdmi@6000000/ports/port@1/endpoint"; hdmi_phy = "/soc/hdmi-phy@6010000"; tcon_top = "/soc/tcon-top@6510000"; tcon_top_mixer0_in = "/soc/tcon-top@6510000/ports/port@0"; tcon_top_mixer0_in_mixer0 = "/soc/tcon-top@6510000/ports/port@0/endpoint@0"; tcon_top_mixer0_out = "/soc/tcon-top@6510000/ports/port@1"; tcon_top_mixer0_out_tcon_tv = "/soc/tcon-top@6510000/ports/port@1/endpoint@2"; tcon_top_hdmi_in = "/soc/tcon-top@6510000/ports/port@4"; tcon_top_hdmi_in_tcon_tv = "/soc/tcon-top@6510000/ports/port@4/endpoint@0"; tcon_top_hdmi_out = "/soc/tcon-top@6510000/ports/port@5"; tcon_top_hdmi_out_hdmi = "/soc/tcon-top@6510000/ports/port@5/endpoint"; tcon_tv = "/soc/lcd-controller@6515000"; tcon_tv_in = "/soc/lcd-controller@6515000/ports/port@0"; tcon_tv_in_tcon_top_mixer0 = "/soc/lcd-controller@6515000/ports/port@0/endpoint"; tcon_tv_out = "/soc/lcd-controller@6515000/ports/port@1"; tcon_tv_out_tcon_top = "/soc/lcd-controller@6515000/ports/port@1/endpoint@1"; rtc = "/soc/rtc@7000000"; r_ccu = "/soc/clock@7010000"; nmi_intc = "/soc/interrupt-controller@7010320"; r_pio = "/soc/pinctrl@7022000"; r_i2c_pins = "/soc/pinctrl@7022000/r-i2c-pins"; r_rsb_pins = "/soc/pinctrl@7022000/r-rsb-pins"; ir = "/soc/ir@7040000"; r_i2c = "/soc/i2c@7081400"; axp313 = "/soc/i2c@7081400/pmic@36"; reg_aldo1 = "/soc/i2c@7081400/pmic@36/regulators/aldo1"; reg_dldo1 = "/soc/i2c@7081400/pmic@36/regulators/dldo1"; reg_dcdc1 = "/soc/i2c@7081400/pmic@36/regulators/dcdc1"; reg_dcdc2 = "/soc/i2c@7081400/pmic@36/regulators/dcdc2"; reg_dcdc3 = "/soc/i2c@7081400/pmic@36/regulators/dcdc3"; r_rsb = "/soc/rsb@7083000"; dump_reg = "/soc/dump_reg@20000"; addr_mgt = "/soc/addr-mgt"; cpu_threshold = "/thermal-zones/cpu-thermal/trips/cpu-trip-0"; cpu_target = "/thermal-zones/cpu-thermal/trips/cpu-trip-1"; cpu_critical = "/thermal-zones/cpu-thermal/trips/cpu-trip-2"; gpu_temp_critical = "/thermal-zones/gpu-thermal/trips/gpu-trip-0"; ve_temp_critical = "/thermal-zones/ve-thermal/trips/ve-trip-0"; ddr_temp_critical = "/thermal-zones/ddr-thermal/trips/ddr-trip-0"; cpu_opp_table = "/opp-table-cpu"; hdmi_con_in = "/connector/port/endpoint"; reg_vcc5v = "/vcc5v"; reg_vcc3v3 = "/vcc3v3"; wifi_pwrseq = "/pwrseq"; }; }; The only useful information that I can seeto my novice eye is: lcd-controller@6515000 { compatible = "allwinner,sun50i-h6-tcon-tv\0allwinner,sun8i-r40-tcon-tv"; reg = <0x6515000 0x1000>; interrupts = <0x00 0x42 0x04>; clocks = <0x02 0x79 0x30 0x00>; clock-names = "ahb\0tcon-ch1"; resets = <0x02 0x36>; reset-names = "lcd"; phandle = <0x7b>; ports { #address-cells = <0x01>; #size-cells = <0x00>; port@0 { reg = <0x00>; phandle = <0x7c>; endpoint { remote-endpoint = <0x31>; phandle = <0x2d>; }; }; port@1 { #address-cells = <0x01>; #size-cells = <0x00>; reg = <0x01>; phandle = <0x7d>; endpoint@1 { reg = <0x01>; remote-endpoint = <0x32>; phandle = <0x2e>; }; }; }; }; Just another hurdle in this long journey! lol But I am learning a lot as I go, so thank you for sticking with me along this journey. Kind regards, Mark -

TX95 Max - Allwinner H618 Quadcore Cortex - A53

AlexYMo99 replied to Mark Waples's topic in Allwinner CPU Boxes

Hi Nick It just so happened that i stumbled uppon a comment of yours mentioning that, so i did exactly that (the only difference being that i did it by renaming and copying the files from the Libreelec github instead of just renaming them) and it worked!. I was even able to flash it to the EMMC with no issues at the moment, the only thing is that the tv box seems to power on randomly after a couple of secconds or gives power to the usb after a while, but i thing that is not related to armbian. Im planning to use it for klipper so it was amazing being able to make it work, you are amazing, really appreciate you man! -

Hi , I have a H96MaxX2 (s905x2) tv box I tried installing armbian but its stuck on starting kernel. Can someone tell me the steps to install it perfectly on my H96MaxX2 (s905x2) Thank you

-

Help wanted to test a new OpenVFD alternative

dfahren replied to Jean-Francois Lessard's topic in Amlogic meson

Yes of course, there is such a file '/boot/armbianEnv.txt', but it is generated on the fly by the Armbian build system and if you don't know this build system in and out, you are pretty easily lost ... You have to set specific environment variables and put the file mentioned in my post in a specific folder and then a valid and correct armbianEnv.txt will be generated by the build system. I'm thinking about how I manage to get this in the standard Armbian build. I don't want to mess with the complex build process only to do something that is very specific for my TV box. -

TX95 Max - Allwinner H618 Quadcore Cortex - A53

AlexYMo99 replied to Mark Waples's topic in Allwinner CPU Boxes

Hi Nick, sorry for joining the conversation with a kinda unrelated topic, I tried your image (24.11.0) in the transpeed h618 tv box and it worked without any issue however wifi doesnt seem to work. I have to say that i havent tried much other than trying the desktop and server images, installing the network manager, etc. Is there anything in particular that i need to do in order to get wifi working?, thanks in advance. -

I have recently purchased a Linux-based TV box with the following specifications: Realtek chipset with the code RTD1395PU 1 GB of RAM (SEC 149 model) 8 GB Flash memory (SCY brand) Operating system: Linux Support for 1 USB, LAN, HDMI I have tried connecting the UART interface to it and observed the boot process using Putty. What I received was a boot system that I will describe later. The issue I'm facing is that there is very little information on the internet about this CPU model, and the support for it is similarly scarce, as it seems to have been discontinued. I can use ESC/Space to access Uboot in the Realtek> prompt, but the number of supported commands is limited. I can still access USB, and of course, I can't use Ctrl+D to stop this process due to copyright issues. Does anyone have any ideas on how to install Armbian from a USB drive onto its flash memory?

-

Description The board has mainline kernel and u-boot support for almost 3 years now but Armbian doesn't build images for it. Add basic build config for this board with Wi-Fi extension enabled. Based on orangepizero2.conf X96 mate is H616-powered TV Box with the same Wi-Fi/BT chip as OPiZ2 (AW859A). Mainline DT is missing Wi-Fi node and some regulators are disabled, but PR is on its way. It doesn't hurt to add Wi-Fi extension to config now. How Has This Been Tested? [x] Compile and verify all defined flavours of image on working hardware [X] Tested Wi-Fi extension with patched DT and proved to be working Checklist: [x] My code follows the style guidelines of this project [x] I have performed a self-review of my own code [x] My changes generate no new warnings View the full article

-

Help wanted to test a new OpenVFD alternative

dfahren replied to Jean-Francois Lessard's topic in Amlogic meson

@Jean-Francois Lessard Thanks for your revised version of your tm16xx driver. I downloaded it from your github repo and installed it in Armbian via a git patch. However, getting the configuration parameter into the driver was (at least for me) quite complicated and took me hours to resolve. But here comes what I found out: You proposed to configure the module parameter in extlinux.conf. Well, there is no such file in the Armbian kernel, or at least I could not find it. If that doesn't work, why not setting up a dedicated tm16xx.conf file in /etc/modprobe.d . I did that, but it has no effect. Once my Tv box boots up, it shows all 8s and all LEDs being on. May be this option works if you use insmod to install the driver, something I don't want to because I want the "boot" writing right at the start. I consulted the documentation of Armbian and found some sections about "armbianEnv.txt". A file in which you can define parameters being passed to the kernel and its modules. That sounds at least promising to me, so I tried to let the Armbian build system set it up for my TV box. Unfortunately, getting such a file accepted by the Armbian build system, which, to say the least, in its complexity IS NOT dumb man's friend .... is harder than one might think. Finally I arrived at a solution and what can I say, "boot" is displayed in the LED line dispaly at the same time the other LEDs of the board also light up. So this solution works. I attach the parameter file to this post. It has to go in the folder "userpatches/bootenv/rk35xx.txt" of the Armbian distribution. So IMHO what remains to do is to amend the patch @jock has published for the current 6.12. Armbian distribution to include the new version of the tm16xx driver from you, Jean-Francois. I thank both of you for being of great help to me. This H96MAXV56 gets better and better and may be one day all features of this TV box run smoothly satisfying everybody. rk35xx.txt

17_53.30_5c62c754.thumb.jpg.09826014d5bed5b5e5c6a1b1f5b48078.jpg)